On 20 January FORTE were invited to run two special sessions at the ICEIC2020 in Barcelona organised by the IEEE. The sessions were on Memristive Device Applications, with the first chaired by Dr Serb, focusing on circuit applications and the second, chaired by Dr Papavassiliou, on neuromorphic applications.

Forte’s three papers are talks are described below.

Memristor-based Reconfigurable Circuits: Challenges in Implementation

Nguyen Dao and Dirk Koch

The emergence of memristor technologies has recently received much attention due to their promising features, expecting to be a key driver in the post-CMOS era. With its ultra-low power, higher density capability and non-volatile characteristics, memristor technology is considered as the best candidate to replace SRAM cells or be employed for routing in digital reconfigurable systems. Although memristor-based reconfigurable circuits can offer many advantages over the conventional CMOS designs, limitations in the utilization of memristor technologies such as electroforming or programming structures have not been thoroughly considered and discussed. This work looks into recent trends in exploiting memristor technologies in reconfigurable circuits and then discusses implementations challenges like memristor programming, reliability and operation of memristor-based memory cells for digitally reconfigurable circuits.

Memristor-enabled Reconfigurable Analog Integrated Circuits

Jakub Szypicyn and Christos Papavassiliou

A design methodology for configurable circuit elements for use in Field Programmable Analogue Arrays is introduced. Memristors are used as analogue memories for the configuration information of adjustable monolithic circuit components, e.g. inductors, capacitors and gain elements. Starting from an adjustable transconductor, two non-trivial building building blocks are developed: a floating capacitor and a floating inductor. Wide frequency response, excellent quality factors and wide adjustability are achieved. To illustrate the capabilities and robustness of our approach a resonator and a simple parametric filter are assembled using the reconfigurable passive circuit elements introduced here. Memristor-enabled tunable blocks have the potential to simplify the design of Field Programmable Analogue Arrays, increase their functionality and, as a result, promote their use. The discrete implementations of reconfigurable components achieve over a decade of component value adjustment range, and operational frequencies to 10s of MHz. Both component adjustment range and other performance metrics are expected to significantly increase in eventual monolithic implementations.

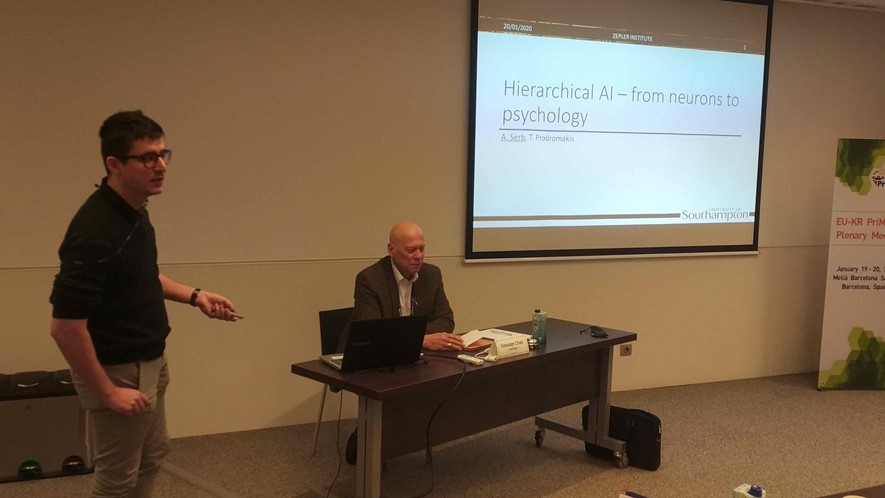

Hierarchical AI - from Neurons to Psychology

The undeniable successes of deep learning (and more generally statistical learning) in bringing pattern matching to the market is still just the tip of the iceberg of AI. In this talk we will look at a very high-level overview of AI as a whole and see how it can be interpreted at very different levels of abstraction. Each level of abstraction boasts its own vocabulary and is suited to understanding different aspects of the general problem of artificial intelligence. Similarly each level has its own limitations in terms of the problems it can attack and its efficiency in doing so. In light of this perspective I shall advocate for a new generation of engineers that can understand AI across all levels of abstraction and is educated for thinking flexibility across the different levels. The hope is that this new approach will unlock the potential of AI to attack problems much more general than simple pattern matching and prepare this new wave of AI for the market.