Open-Source RRAM Compiler

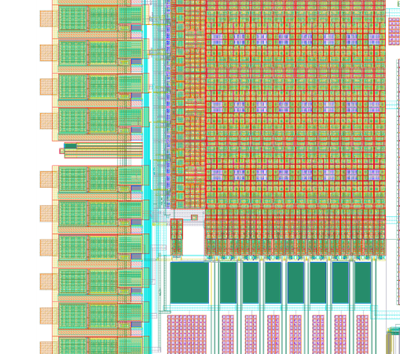

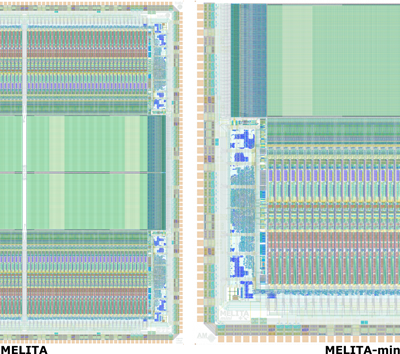

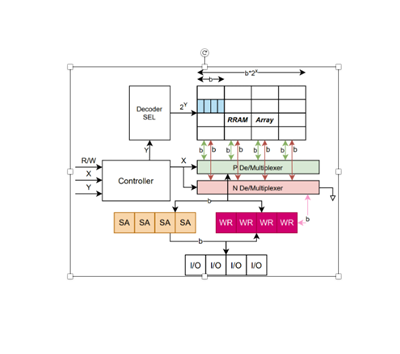

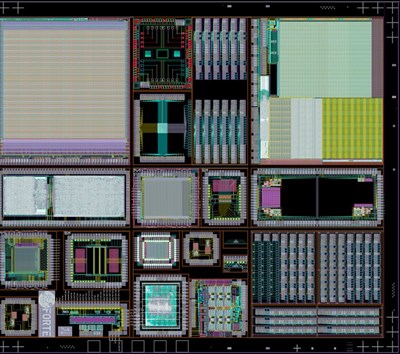

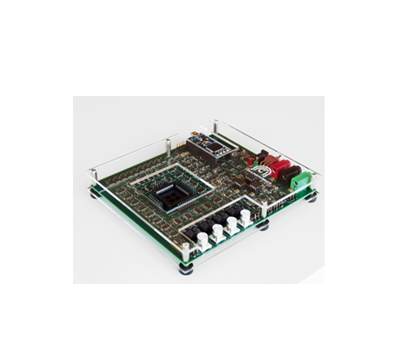

Memory compilers are necessary tools to boost the design procedure of digital circuits. However, only a few are available to academia. Resistive Random Access Memory (RRAM) is characterised by high density, high speed, non volatility and is a potential candidate of future digital memories. To the best of the authors' knowledge, this paper presents the first open source RRAM compiler for automatic memory generation including its peripheral circuits, verification and timing characterisation. The RRAM compiler is written with Cadence SKILL programming language and is integrated in Cadence environment. The layout verification procedure takes place in Siemens Mentor Calibre tool. The technology used by the compiler is TSMC 180nm. This paper analyses the novel results of a plethora of M x N RRAMs generated by the compiler, up to M = 128, N = 64 and word size B = 16 bits, for clock frequency equal to 12.5 MHz. Finally, the compiler achieves density of up to 0.024 Mb/mm2.